Что означает risc архитектура микроконтроллера

Национальная библиотека им. Н. Э. Баумана

Bauman National Library

Персональные инструменты

RISC (Reduced Instruction Set Computing)

RISC (англ. Restricted (reduced) Instruction Set Computer — «компьютер с сокращённым набором команд») — архитектура процессора, в котором быстродействие увеличивается за счёт упрощения инструкций, чтобы их декодирование было более простым, а время выполнения — меньшим. Термин «сокращённый» в названии описывает тот факт, что сокращён объём (и время) работы, выполняемый каждой отдельной инструкцией — как максимум один цикл доступа к памяти.

Содержание

Характерные особенности RISC-процессоров

Преимущества RISC

История RISC

Предпосылки развития RISC архитектур:

Начало исследований

Первая система, которая может быть названа системой «RISC», — суперкомпьютер «CDC 6600», который был создан в 1964 году, за десять лет до появления соответствующего термина. CDC 6600 имел архитектуру «RISC» всего с двумя режимами адресации («регистр+регистр» и «регистр+непосредственное значение») и 74 кодами команд (тогда как 8086 имел 400 кодов команд). В «CDC 6600» было 11 конвейерных устройств арифметической и логической обработки, а также пять устройств загрузки и два устройства хранения. Память была много блочной, поэтому все устройства загрузки-хранения могли работать одновременно. Базовая тактовая частота/частота выдачи команд была в 10 раз выше, чем время доступа к памяти. Джим Торнтон и Сеймур Крэй, разработчики «CDC 6600», создали для него мощный процессор, позволявший быстро обрабатывать большие объёмы цифровых данных. Главный процессор поддерживался десятью простыми периферийными процессорами, выполнявшими операции ввода-вывода и другие функции ОС. Позднее появилась шутка, что термин «RISC» на самом деле расшифровывается как «Really invented by Seymour Cray» (пер. с англ.: «на самом деле придуман Сеймуром Крэем»).

Если быть уж совсем точным, то первой компанией, начавшей разработку RISC-архитектуры, стала IBM. Еще в 1974 году стартовала разработка процессора IBM 801, которая и заложила первые основы для этой платформы. А проект Berkeley RISC окончательно сформировал архитектуру. Все х86-процессоры, решения компании Motorola и подавляющее большинство выпущенных в 1980-е годы кристаллов имели архитектуру CISC (Complex Instruction Set Computing). Совокупность всех особенностей привела к тому, что чипы стали не только сложными и дорогими в производстве, но и достигли своего потолка производительности. Для дальнейшего увеличения быстродействия требовалось наращивать количество транзисторов, однако освоенные технологические нормы не позволяли создавать более сложные решения. С этим столкнулась Intel при выпуске семейства i486. Для поднятия производительности они внесли изменения в архитектуру процессоров, добавив кэш-память, множители и конвейеры. Словом, 486-е «камни» получили некоторые «фишки» архитектуры RISC. Тем не менее к созданию RISC-платформы американская компания никакого отношения не имеет. Своим созданием архитектура обязана американскому инженеру Дэвиду Паттерсону, который руководил проектом Berkeley RISC с 1980 по 1984 годы.

Первоначальной идеей, которая затем воплотилась в столь масштабный проект Berkeley RISC, стало исследование работы Motorola 68000. В ходе наблюдений выяснилось, что программы попросту не использовали подавляющее большинство инструкций, заложенных в процессор. Например, система Unix при компиляции использовала лишь 30% команд. Поэтому в рамках проекта Berkeley RISC планировалось создать такой процессор, который бы содержал лишь самые необходимые инструкции.

Дебютными решениями стали RISC I и RISC II — детища Паттерсона и проекта Berkeley RISC. Первый содержал более чем 44 000 транзисторов и работал на частоте 4 МГц. Такой процессор при выполнении небольших программ был в среднем в два раза быстрее VAX 11/780 и примерно в четыре раза производительнее, чем «камень» Zilog Z8000. RISC II отличался от предшественника большим количеством инструкций: 39 против 32. Он был более быстрым. Его преимущество над процессором VAX достигало 200%, а Motorola 68000 в некоторых программах был медленнее примерно в четыре раза.

Программа, ограниченная лишь восемью регистрами для каждой процедуры, может выполнять очень быстрые вызовы процедур: «окно» просто сдвигается к 8-регистровому блоку нужной процедуры, а при возврате из процедуры сдвигается обратно, к регистрам вызвавшей процедуры. (В обычном процессоре большинство процедур при вызове вынуждены сохранять значения некоторых регистров в стеке для того, чтобы пользоваться этими регистрами при исполнении процедуры. При возврате из процедуры значения регистров восстанавливаются из стека).

Практически в то же время, в 1981 году, Джон Хеннесси начал аналогичный проект, названный «архитектура „MIPS“» в Стэнфордском университете. Создатель «MIPS» практически полностью сфокусировался на конвейерной обработке, попытавшись «выжать всё» из этой технологии. Конвейерная обработка использовалась и в других продуктах, некоторые идеи, реализованные в MIPS, позволили разработанному чипу работать значительно быстрее аналогов. Наиболее важным было требование выполнения любой из инструкций процессора за один такт. Это требование позволило конвейеру работать на гораздо больших скоростях передачи данных и привело к значительному ускорению работы процессора. С другой стороны, исполнение этого требования имело негативный побочный эффект в виде удаления из набора инструкций таких полезных операций, как умножение или деление. В первые годы попытки развития архитектуры «RISC» были хорошо известны, однако оставались в рамках породивших их университетских исследовательских лабораторий. Многие в компьютерной индустрии считали, что преимущества процессоров «RISC» не проявятся при использовании в реальных продуктах из-за низкой эффективности использования памяти в составных инструкциях. Однако с 1986 года исследовательские проекты «RISC» начали выпускать первые работающие продукты.

Последние разработки

В 1985 году IBM начала разработку RISC-архитектуры следующего поколения. Проект получил название America Project. Разработка процессора и набора инструкций для него закончилась в 1990 году. Сам кристалл получил название POWER1 и использовался в серверах и рабочих станциях IBM. Он обладал достаточно высоким уровнем производительности, но имел многочиповую компоновку и состоял из 11 различных микросхем. В 1992 году IBM представила бюджетный вариант процессора POWER1, который умещался в одном чипе.

Как оказалось в начале 1990-х годов, RISC-архитектуры позволяют получить большую производительность, чем CISC, за счёт использования суперскалярного и VLIW-подхода, а также за счёт возможности серьёзного повышения тактовой частоты и упрощения кристалла с высвобождением площади под кэш, достигающий огромных ёмкостей. Также RISC-архитектуры позволили сильно снизить энергопотребление процессора за счёт уменьшения числа транзисторов. Первое время RISC-архитектуры с трудом принимались рынком из-за отсутствия программного обеспечения для них. Эта проблема была решена переносом UNIX-подобных операционных систем (SunOS) на RISC-архитектуры.

В настоящее время многие архитектуры процессоров являются RISC-подобными, к примеру, ARM, DEC Alpha, SPARC, AVR, MIPS, POWER и PowerPC. Наиболее широко используемые в настольных компьютерах процессоры архитектуры x86 ранее являлись CISC-процессорами, однако новые процессоры, начиная с Intel Pentium Pro, являются CISC-процессорами с RISC-ядром. Они непосредственно перед исполнением преобразуют CISC-инструкции x86-процессоров в более простой набор внутренних инструкций RISC. После того, как процессоры архитектуры x86 были переведены на суперскалярную RISC-архитектуру, можно сказать, что большинство существующих ныне процессоров основаны на архитектуре RISC.

Мобильные системы

Суперкомпьютеры

Характеристики

Распространенное заблуждение «компьютер с сокращенным набором команд» ошибочно наводит на мысль, что инструкции просто устранены, в результате меньшего набора инструкций. На самом деле, на протяжении многих лет, наборы команд RISC выросли в размерах, и сегодня многие из них имеют больший набор инструкций, чем многие CISC процессоры. Некоторые процессоры RISC, такие как PowerPC имеют наборы инструкций, большие, чем в CISC IBM System/370.

Процессоры также имели относительно небольшое число регистров, по нескольким причинам:

В первые дни компьютерной индустрии, программирование было сделано в ассемблере или машинном коде, который поощрял мощные и простые в использовании инструкции. Поэтому конструкторы CPU пытались сделать инструкции, которые будут делать столько работы, сколько возможно. С появлением высокоуровневых языков, компьютерные архитекторы начали создавать специальные инструкции непосредственно реализующие определенные центральные механизмы таких языков. Еще одна общая цель состояла в том, чтобы обеспечить все возможные режим адресации для каждой команды, известной как ортогональность, чтобы облегчить реализацию компилятора. Поэтому арифметические операции могут часто имеют результаты, а также операнды непосредственно в памяти.

Гениальность микропроцессоров RISC-V

Войны между RISC и CISC, проходившие в конце 1990-х, уже давно отгремели, и сегодня считается, что разница между RISC и CISC совершенно не имеет значения. Многие заявляют, что наборы команд несущественны.

Однако на самом деле наборы команд важны. Они накладывают ограничения на типы оптимизаций, которые можно легко добавлять в микропроцессор.

Недавно я подробнее изучил информацию об архитектуре набора команд (instruction-set architecture, ISA) RISC-V и вот некоторые из аспектов, которые по-настоящему впечатлили меня в ISA RISC-V:

Месть RISC

Когда я начал понимать RISC-V лучше, то осознал, что RISC-V оказался радикальным возвратом к тому, что многие считали давно прошедшей эпохой вычислений. С точки зрения конструкции, RISC-V подобен перемещению на машине времени к классическому Reduced Instruction Set Computer (RISC, «компьютеру с набором коротких команд») начала 80-х и 90-х.

В последние годы многие заявляли, что разделение на RISC и CISC больше не имеет смысла, поскольку в процессоры RISC наподобие ARM добавили так много команд, и при этом многие из них довольно сложны, что на текущем этапе это скорее гибрид, чем чистый процессор RISC. Похожие рассуждения применялись и к другим процессорам RISC, например, PowerPC.

RISC-V же, напротив, является действительно «хардкорным» представителем процессоров RISC. Если вы почитаете в Интернете обсуждения RISC-V, то найдёте людей, утверждающих, что RISC-V был разработан какими-то олдскульными RISC-радикалами, отказывающимися двигаться в ногу со временем.

Бывшая инженер ARM Эрин Шеперд несколько лет назад написала интересную критику RISC-V:

ISA RISC-V слишком стремился к минимализму. В нём есть сильный упор на минимизацию количества команд, нормализацию кодирования и т.д. Это стремление к минимализму привело к ложным ортогональностям (например, использованию одной и той же команды для ветвления, вызовов и возвратов) и требованию избыточных команд, влияющих на плотность кода с точки зрения размера и количества команд.

Вкратце приведу немного контекста. Малый размер кода даёт преимущество в производительности, поскольку так проще хранить выполняемый код внутри высокоскоростного кэша процессора.

Критика здесь заключается в том, что проектировщики RISC-V слишком сосредоточились на обеспечении малого набора команд. В конце концов, это ведь одна из исходных целей RISC.

По словам Эрин, следствием этого стало то, что реальной программе для выполнения задач потребуется гораздо больше команд, то есть она займёт больше места в памяти.

Традиционно долгие годы считалось, что в процессор RISC нужно добавить больше команд, чтобы он стал более похожим на CISC. Идея заключается в том, что более специализированные команды могут заменить использование множественных общих команд.

Сжатие команд и Macro-Operation Fusion

Однако в архитектуре процессоров присутствуют две инновации, из-за которых эта стратегия добавления более сложных команд во многих смыслах оказывается избыточной:

Однако тут есть тонкость: RISC-V получает из этих двух стратегий гораздо больше выгод по двум важным причинам:

Так как в команде нужно указать три разных регистра, то для кодирования операндов (входящих данных для операции сложения) требуется в сумме 15 бит (3 × 5).

Следовательно, чем больше возможностей мы хотим поддерживать в наборе команд, тем больше битов мы займём из доступных нам 32 бит. Разумеется, мы можем перейти к 64-битным командам, но при этом потратится слишком много памяти, а значит, пострадает производительность.

Агрессивно стремясь к сохранению малого количества команд, RISC-V оставляет больше места для добавления битов, обозначающих, что мы используем сжатые команды. Если процессор видит, что в команде заданы определённые биты, то он понимает, что её нужно интерпретировать как сжатую.

Это означает, что вместо засовывания внутрь 32 бит одной команды мы можем уместить две команды по 16 бит шириной каждая. Естественно, не все команды RISC-V можно выразить в 16-битном формате. Поэтому подмножество 32-битных команд выбирается на основании их полезности и частоты использования. Если несжатые команды могут получать 3 операнда (входящих данных), то сжатые команды — только 2 операнда. То есть сжатая команда ADD будет выглядеть так:

По сути, сжатые команды уменьшают количество операндов. Три регистра-операнда заняли бы 15 бит, оставив на указание операции всего 1 бит! Таким образом, при использовании двух операндов для указания опкода (выполняемой операции) у нас остаётся 6 бит.

На самом деле это близко к тому, как работает ассемблер x86, когда зарезервировано недостаточно битов для использования трёх регистров-операндов. Процессор x86 при этом тратит биты, чтобы позволить, например, команде ADD считывать входящие данные и из памяти, и из регистров.

Однако истинную выгоду мы получаем, объединив сжатие команд с Macro-operation fusion. Когда процессор получает 32-битное слово, содержащее две сжатые 16-битные команды, он может слить их в одну более сложную команду.

Звучит, как чушь — мы что, вернулись к тому, с чего начинали?

Нет, поскольку мы минуем необходимость заполнения спецификации ISA кучей сложных команд (то есть стратегии, которой придерживается ARM). Вместо этого мы, по сути, выражаем целое множество сложных команд косвенно, через различные сочетания простых команд.

В обычных условиях Macro-fusion вызвало бы проблему: хотя две команды заменяются одной, они всё равно занимают в два раза больше памяти. Однако при сжатии команд мы не занимаем никакого лишнего места. Мы пользуемся преимуществами обеих архитектур.

Давайте рассмотрим один из примеров, приведённых Эрин Шеперд. В своей критической статье о ISA RISC-V она показывает простую функцию на C. Чтобы было понятнее, я взял на себя смелость переписать её:

На x86 это скомпилируется в следующий ассемблерный код:

На ARM всё происходит похожим образом:

Здесь мы не умножаем на 4, а сдвигаем регистр r1 на 2 бита влево, что эквивалентно умножению на 4. Вероятно, это более верное описание и того, что происходит на x86. Сомневаюсь, что можно умножать на что-либо, не являющееся кратным 2, поскольку умножение — это довольно сложная операция, а сдвиг малозатратен и прост.

Из моего описания x86 об остальном можно только догадываться. Теперь давайте перейдём к RISC-V, где начинается настоящее веселье! (точкой с запятой начинаются комментарии)

И всё это выглядит совершенно ужасно, правда? Вдвое больше команд для такой простой и часто используемой операции, как выполнение поиска по индексу в таблице и возврат результата.

Это действительно выглядит плохо. Именно поэтому Эрин Шеперд чрезвычайно критически отнеслась к проектировочным решениям, сделанным разработчиками RISC-V. Она пишет:

Упрощения RISC-V делают более простым декодер (т.е. фронтенд процессора), однако за это приходится расплачиваться бо́льшим количеством команд. Однако масштабирование ширины конвейера — это сложная задача, в то время как декодирование немного (или сильно) необычных команд хорошо изучено (основные сложности возникают, когда определение длины команды нетривиально — из-за своих бесконечных префиксов особо запущенным случаем является x86).

Однако благодаря сжатию команд и macro-op fusion можно изменить ситуацию к лучшему.

Теперь команды занимают ровно столько же места в памяти, что и пример для ARM.

Так, а теперь давайте выполним Macro-op fusion!

Одно из условий RISC-V для разрешения слияния операций в одну — это совпадение целевого регистра. Это условие выполняется для команд ADD и LW (load word, «загрузить слово»). Поэтому процессор превратит их в одну команду.

Если бы это условие выполнялось и для SLLI, то мы могли бы слить в одну все три команды. То есть процессор бы увидел нечто, напоминающее более сложную команду ARM:

Но почему мы не могли прописать эту сложную макро-операцию непосредственно в коде?

Потому что в ISA нет поддержки такой макро-операции! Вспомним, что у нас есть ограниченное количество битов. Тогда сделаем команды длиннее! Нет, это займёт слишком много памяти и быстрее переполнит драгоценный кэш процессора.

Однако если вместо этого мы будем изготавливать эти длинные полусложные команды внутри процессора, то никаких проблем не возникает. У процессора никогда не бывает одновременно в наличии более нескольких сотен команд. Поэтому если мы потратим на каждую команду, допустим, 128 бит, то это не создаст затруднений. Кремния по-прежнему будет хватать на всё.

Когда декодер получает обычную команду, он обычно превращает её в одну или несколько микро-операций. Такие микро-операции и есть команды, с которыми на самом деле работает процессор. Они могут быть очень широкими и содержат множество дополнительной полезной информации. Приставка «микро» звучит иронично, ведь они оказываются шире. Однако на самом деле «микро» означает, что они имеют ограниченное количество задач.

Macro-operation fusing немного переворачивает работу декодера вниз головой: вместо превращения одной команды в несколько микро-операций, мы берём много операций и превращаем их в одну микро-операцию.

То есть происходящее в современном процессоре может выглядеть довольно странно:

Ключевым аспектом перехода к микро-операциям является нужный уровень сложности:

Получаемые преимущества

Мы обсудили множество подробностей, поэтому сейчас вам, должно быть, трудно понять, в чём смысл всех этих трудов. Зачем нужны все эти сжатия и слияния? Похоже, что из-за них выполняется много лишней работы.

Во-первых, сжатие команд совершенно не походит на сжатие zip. Слово «сжатие» немного неверное, потому что мгновенное сжатие или распаковка команды выполняются абсолютно просто. На это не тратится времени.

То же самое относится к macro-operation fusion. Хотя этот процесс может казаться сложным, подобные системы уже используются в современных микропроцессорах. Поэтому затраты, которые добавляет вся эта сложность, уже были оплачены.

Однако в отличие от проектировщиков ARM, MIPS и x86, приступая к проектированию своего ISA, создатели RISC-V знали о сжатии команд и macro-ops fusion. Благодаря различным тестам с первым минимальным набором команд они сделали два важных открытия:

Это заставило коллектив разработчиков RISC-V удвоить усилия по реализации macro-operation fusion как фундаментальной стратегии RISC-V. В руководстве по RISC-V есть множество примечаний о том, с какими операциями можно выполнять слияние. Также в него внесены правки, упрощающие слияние команд, встречающихся в частых паттернах.

Благодаря малому ISA его проще изучать студентам. А это означает, что изучающему процессорные архитектуры студенту проще спроектировать собственный процессор, работающий на командах RISC-V. Стоит помнить, что и сжатие команд, и macro-op fusion использовать необязательно.

RISC-V имеет небольшой фундаментальный набор команд, реализация которого обязательна. Однако все остальные команды реализуются как части расширений. Сжатые команды — это просто дополнительное расширение.

Macro-op fusion — это просто оптимизация. Она не меняет поведения в целом, а поэтому её необязательно реализовывать в собственном процессоре RISC-V.

Стратегия проектирования RISC-V

RISC-V взял всё, что мы знаем сегодня о современных процессорах, и использовал эти знания в проектировании процессоров ISA. Например, мы знаем, что:

Изначально условное выполнение создавалось для того, чтобы избегать ветвлений, потому что они плохо влияют на конвейеры. Для ускорения работы процессора он обычно заранее получает следующие команды, чтобы сразу после выполнения предыдущей на первой стадии процессора можно было подхватить следующую.

При условном ветвлении мы не можем заранее знать, где будет следующая команда, когда начинаем заполнять конвейер. Однако суперскалярный процессор может просто выполнять обе ветви параллельно.

Именно из-за этого RISC-V не имеет и регистров состояния, ведь они создают зависимости между командами. Чем более независима каждая команда, тем проще выполнять её параллельно с другой командой.

По сути, стратегия RISC-V заключается в том, что мы можем сделать ISA как можно более простым, а минимальную реализацию процессора RISC-V как можно более простой без необходимости принятия конструкторских решений, из-за которых невозможно будет создать высокопроизводительный процессор.

На правах рекламы

Наша компания предлагает серверы не только с CPU от Intel, но и серверы с процессорами AMD EPYC. Как и для других типов серверов, огромный выбор операционных систем для автоматической установки, есть возможность установить любую ОС с собственного образа. Попробуйте прямо сейчас!

Не хотите RISCовать? Узнайте больше о процессорах архитектуры RISC

Что такое RISC-архитектура? Краткая история

Аббревиатура «RISC», от английского — reduced instruction set computer, переводится на русский как «сокращенное (ограниченное) число команд (инструкций)».

Очень часто в каталогах продукции различных производителей можно встретить название раздела или описание товара с указанием «на базе RISC». Данное заявление не относится к описанию каких-либо особых функций или характеристик оборудования. Оно связано только с одним из важнейших элементов любой ЭВМ, ее «вычислительным сердцем», без которого, не может функционировать ни один компьютер в мире. Указывая «RISC», производитель подразумевает только одно – процессор.

Похожие публикации

Встраиваемый многослотовый ПК IPC970 с поддержкой высокопроизводительных процессоров и видеокарт

Обновление линейки безвентиляторных панельных ПК XPPC от Nexcom

Панельные ПК VMC 2020 и VMC 220 от Nexcom для эксплуатации на транспорте

Свое начало «RISC» архитектура процессоров берет в середине 70-х – 80-х годов. Исследователями того времени, в частности представители IT-гиганта IBM, было выяснено, что большинство комбинаций команд и прямых методов адресации, не были задействованы использовавшимися в то время компиляторами («сборщики» исходного программного кода высокого уровня в программу на машинном языке, «понятную» компьютеру). Кроме того, было обнаружено, что программы, реализующие набор инструкций актуальных процессоров, зачастую обрабатывают сложные операции значительнее медленнее простых, выполняющие те же действия. Основная проблема заключалась в общей оптимизации микрокода процессора. Для решения простых задач процессоры того времени представляли из себя слишком сложные устройства, содержащие в себе большое количество инструкций, половина которых, могла даже быть не задействована. Соответственно, обработка всех инструкций сказывалась и на общей производительности процессора. Учтя все минусы современных процессоров того времени, было принято решение о разработке новой архитектуры. Основной фокус – сделать инструкции процессора настолько простыми, чтобы они легко и эффективно конвейеризировались (технология организации вычислений в процессорах и контроллерах). После нескольких лет исследований, в начале 80-х годов, было выпущено несколько видов процессоров, общее название которых и дало имя всей архитектуры – RISC. Своим созданием новая архитектура обязана американскому инженеру Дэвиду Паттерсону, руководителю проекта Berkeley RISC с 1980 по 1984 годы. В рамках данного проекта были разработаны дебютные процессоры новой архитектуры — RISC I и RISC II.

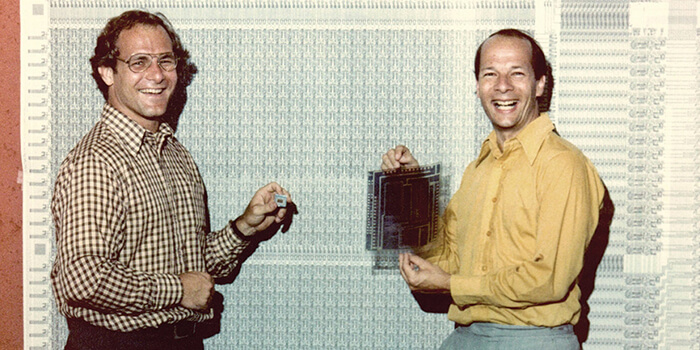

Профессора кафедры «Электротехника и компьютерные науки (EECS)» калифорнийского университета в Беркли, слева направо, Дэвид Паттерсон и Карло Секин. Участники проекта «Berkeley RISC». (ссылка на источник)

CISC и RISC процессоры. Характерные отличия, преимущества и недостатки

Все процессоры в мире, условно можно поделить на два типа – RISC, о нем уже было ранее сказано, и CISC. Что же такое CISC-процессор? Аббревиатура «CISC», от английского complete instruction set computing, переводится как «полный набор команд (инструкций)».

Главные особенности, определяющие архитектуру CISC:

CISC-процессоры являются так называемыми «классическими» процессорами. Они содержат в сотни раз больше команд, чем RISC-архитектура, используют больше способов адресации и т.д. На рубеже 80—90-ых в мире разгорелся настоящий «жаркий» спор, о том, какой же процессор лучше? С одной стороны баррикад, поставщики процессоров RISC — Hewlett-Packard (PA-RISC), Sun Microsystems Computers (SPARC), Silicon Graphics (MIPS) (R210000), союз IBM и Motorola (PowerPC), с другой – Intel и AMD. И решение было найдено не в технических аргументах сторон, а в технологическом преимуществе Intel и AMD. Но, с начала 2000-х, с момента появления мобильных решений и стремительного скачка развития в этом сегменте технологий, архитектура RISC обрела новую жизнь. Кроме того, во многих современных процессорах CISC, отдельные блоки и модули инструкций, представляют из себя, не что иное как RISC-процессор.

Наглядное сравнение процессоров CISС и RISC архитектур. CISC – массивный, мощный Кадиллак с эффектными спойлерами. RISC – быстрый, маневренный, компактный Porsche. (Из выступления Дэвида Паттерсона в 1985 году,ссылка).

В данной части мы не будем подробно рассматривать технические характеристики процессоров RISC, основные принципы построения архитектуры, алгоритмы логики и т.д. На данную тему, в просторах интернета, можно найти множество различных статей, как в англоязычном, так и в русскоязычном сегменте. Нас же, в первую очередь интересует вопрос – «Что получит обычный пользователь, приобретая оборудования на базе архитектуры RISС процессора?». Именно этот вопрос, послужит основным тезисом при разборе преимуществ и недостатков далее.

Преимущества

К сожалению, недостатки RISC процессоров, тесно связаны с их преимуществами.

Недостатки

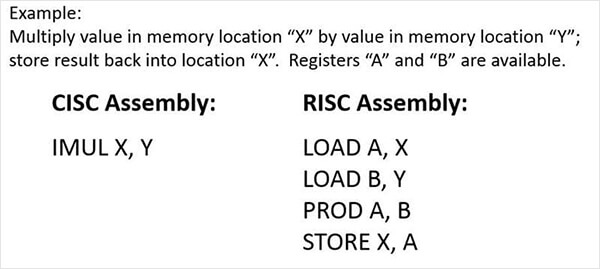

Простой пример сравнения СISC-кода и RISC-кода.

Основные RISC-процессоры. Что применяют в промышленности?

Как уже упоминалось выше, на сегодняшний день, RISС-подобные процессоры активно развиваются в своем сегменте рынка. Большую часть этого сегмента, 80%-90% занимают процессоры для товары широкого потребления. Конечно же, это различные смартфоны, планшетные компьютеры, игровые приставки и т.д. Любое мобильное устройство, где необходимо использование процессора, с вероятностью 90% построено на вычислительной мощности RISC-подобного процессора. Но, возможно Вы об этом не слышали и сам термин «RISC-подобный» вызывает дополнительные вопросы. Неоднократно в данной статье говорилось о RISC-подобных процессорах, что же это такое? RISC-подобные процессоры – это процессоры, в базисе архитектуры которых, были заложены основные идеи при разработке первых RISC процессоров, но в дальнейшем, приобретали свои уникальные свойства, особенности и развивались уже собственным путем. Инженеры-разработчики данных процессоров, черпали вдохновение именно из идей проекта «Berkeley RISC». Самые известные архитектуры RISC-подобных процессоров это ARM, MIPS, SPARK. Но конечно же есть и другие, менее распространённые, либо применяемые только в специализированных сферах, такие как – SuperH (SH), PowerPC, AVR и другие. Даже Intel и AMD разработали некогда свою собственную архитектуру на RISC-ядре – Intel P5/P6 и AMD K5/K6/K7. Но, стоит сказать об интересной особенности, данные компании занимаются лишь проектированием и лицензированием микропроцессорных устройств, но своих производственных мощностей не имеют. Например, лицензиатами архитектуры ARM, являются такие известные мировые производителя как AMD, Apple, Samsung, Qualcomm, Sony, HiSilicon и многие другие. Соответственно, такие современные процессоры как Snapdragon 865, Kirin 980, Samsung Exynos Octa 990 и Apple A12Z, разработаны на ARM-микропроцессоре. Самые известные производители, использующие в своих процессорах MIPS архитектуру, это Realtek, Broadcom, Atheros, ATI, Toshiba и российская компания «Т-Платформа», использующий процессорные ядра P5600 архитектуры MIPS32 Release 5 в процессоре Baikal-T1. Как мы можем увидеть, рынок RISC-подобных процессоров в массовом сегменте достаточно широкий, и можно найти решения отвечающее любым задач, но как обстоят дела в промышленном сегменте?

Особенности промышленных компьютеров RISC

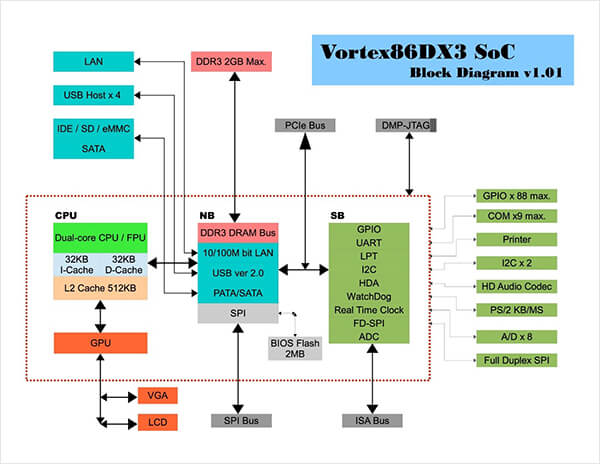

Развитие RISC-подобных процессоров в промышленной отрасли отличается от массового рынка. В первую очередь это связано с не таким огромным спросом на устройства с данным типом процессора. Если у производителя есть возможности, он может реализовать в своем устройстве уже готовое процессорное ядро от стороннего разработчика и в дальнейшем просто оптимизировать под него программное обеспечение. Чаще всего так и происходит и самые распространённым для применения процессором в данном контексте является Cortex, являющийся процессором ARM архитектуры от разработчика ARM Holdings. Более сложный путь, иметь собственный процессор, развитие и разработка которого полностью зависят от самого производителя. Одним из таких производителей является компания DMP, которая выпускает процессоры собственной линейки под названием Vortex86. Процессоры серии Vortex86 являются процессорами так называемой «системой на кристалле» (от. System-on-a-Chip, SoC), т.е. один чип включающий в себя CPU, North Bridge и South Bridge.

Блок-диаграмма процессора Vortex86DX3.

На базе данного семейства процессоров подразделение производителя DMP, компанияiCOP, разрабатывает и выпускает промышленное оборудование различного форм-фактора. У компании есть три основные линейки, каждая из которых включает различные варианты конфигураций и функционала для задач любой сложности.

Так какие же основные преимущества у промышленных компьютеров на базе процессоров RISC? Перечислим их по пунктам:

Особенности промышленных компьютеров RISC

С момента своего появления и до сегодняшних дней, эволюция процессоров RISC сделала гигантский скачок вперед и запас потенциала их дальнейшего развития еще очень и очень велик. С появления узкоспециализированных процессоров в рамках закрытых научных программ до базовой вычислительной основы миллионов устройств по всему миру, кажется, прошло совсем немного времени, но данный промежуток ярко показывает насколько это была гениальная инженерная мысль с последующим ее огромным влиянием на развитие всей IT-индустрии.