Что поступает в процессор

Как работает процессор?

Авторизуйтесь

Как работает процессор?

Инструмент проще, чем машина. Зачастую инструментом работают руками, а машину приводит в действие паровая сила или животное.

Компьютер тоже можно назвать машиной, только вместо паровой силы здесь электричество. Но программирование сделало компьютер таким же простым, как любой инструмент.

Процессор — это сердце/мозг любого компьютера. Его основное назначение — арифметические и логические операции, и прежде чем погрузиться в дебри процессора, нужно разобраться в его основных компонентах и принципах их работы.

Два основных компонента процессора

Устройство управления

Устройство управления (УУ) помогает процессору контролировать и выполнять инструкции. УУ сообщает компонентам, что именно нужно делать. В соответствии с инструкциями он координирует работу с другими частями компьютера, включая второй основной компонент — арифметико-логическое устройство (АЛУ). Все инструкции вначале поступают именно на устройство управления.

Существует два типа реализации УУ:

УУ на жёсткой логике быстрее, но УУ с микропрограммным управлением обладает более гибкой функциональностью.

Арифметико-логическое устройство

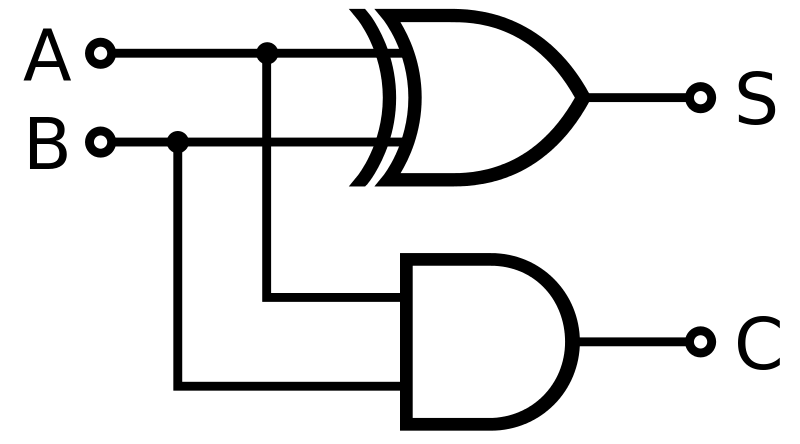

Это устройство, как ни странно, выполняет все арифметические и логические операции, например сложение, вычитание, логическое ИЛИ и т. п. АЛУ состоит из логических элементов, которые и выполняют эти операции.

20–22 декабря, Онлайн, Беcплатно

Большинство логических элементов имеют два входа и один выход.

Ниже приведена схема полусумматора, у которой два входа и два выхода. A и B здесь являются входами, S — выходом, C — переносом (в старший разряд).

Схема арифметического полусумматора

Хранение информации — регистры и память

Как говорилось ранее, процессор выполняет поступающие на него команды. Команды в большинстве случаев работают с данными, которые могут быть промежуточными, входными или выходными. Все эти данные вместе с инструкциями сохраняются в регистрах и памяти.

Регистры

Регистр — минимальная ячейка памяти данных. Регистры состоят из триггеров (англ. latches/flip-flops). Триггеры, в свою очередь, состоят из логических элементов и могут хранить в себе 1 бит информации.

Прим. перев. Триггеры могут быть синхронные и асинхронные. Асинхронные могут менять своё состояние в любой момент, а синхронные только во время положительного/отрицательного перепада на входе синхронизации.

По функциональному назначению триггеры делятся на несколько групп:

Для хранения промежуточных данных ОЗУ не подходит, т. к. это замедлит работу процессора. Промежуточные данные отсылаются в регистры по шине. В них могут храниться команды, выходные данные и даже адреса ячеек памяти.

Принцип действия RS-триггера

Память (ОЗУ)

ОЗУ (оперативное запоминающее устройство, англ. RAM) — это большая группа этих самых регистров, соединённых вместе. Память у такого хранилища непостоянная и данные оттуда пропадают при отключении питания. ОЗУ принимает адрес ячейки памяти, в которую нужно поместить данные, сами данные и флаг записи/чтения, который приводит в действие триггеры.

Прим. перев. Оперативная память бывает статической и динамической — SRAM и DRAM соответственно. В статической памяти ячейками являются триггеры, а в динамической — конденсаторы. SRAM быстрее, а DRAM дешевле.

Команды (инструкции)

Команды — это фактические действия, которые компьютер должен выполнять. Они бывают нескольких типов:

Прим. перев. На самом деле все арифметические операции в АЛУ могут быть созданы на основе всего двух: сложение и сдвиг. Однако чем больше базовых операций поддерживает АЛУ, тем оно быстрее.

Инструкции предоставляются компьютеру на языке ассемблера или генерируются компилятором высокоуровневых языков.

В процессоре инструкции реализуются на аппаратном уровне. За один такт одноядерный процессор может выполнить одну элементарную (базовую) инструкцию.

Группу инструкций принято называть набором команд (англ. instruction set).

Тактирование процессора

Быстродействие компьютера определяется тактовой частотой его процессора. Тактовая частота — количество тактов (соответственно и исполняемых команд) за секунду.

Частота нынешних процессоров измеряется в ГГц (Гигагерцы). 1 ГГц = 10⁹ Гц — миллиард операций в секунду.

Чтобы уменьшить время выполнения программы, нужно либо оптимизировать (уменьшить) её, либо увеличить тактовую частоту. У части процессоров есть возможность увеличить частоту (разогнать процессор), однако такие действия физически влияют на процессор и нередко вызывают перегрев и выход из строя.

Выполнение инструкций

Инструкции хранятся в ОЗУ в последовательном порядке. Для гипотетического процессора инструкция состоит из кода операции и адреса памяти/регистра. Внутри управляющего устройства есть два регистра инструкций, в которые загружается код команды и адрес текущей исполняемой команды. Ещё в процессоре есть дополнительные регистры, которые хранят в себе последние 4 бита выполненных инструкций.

Ниже рассмотрен пример набора команд, который суммирует два числа:

Вот такие операции нужны, чтобы сложить два числа.

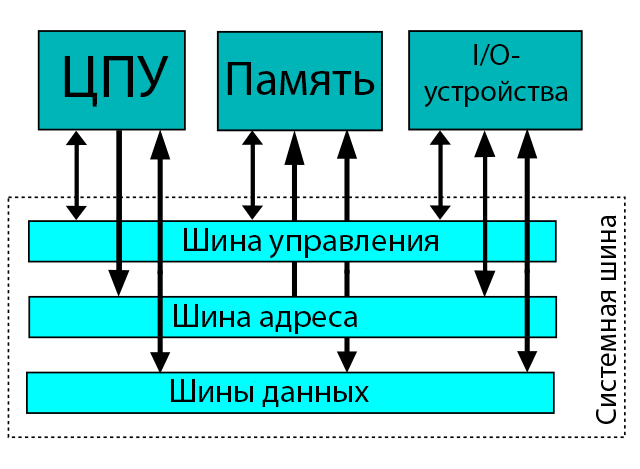

Все данные между процессором, регистрами, памятью и I/O-устройствами (устройствами ввода-вывода) передаются по шинам. Чтобы загрузить в память только что обработанные данные, процессор помещает адрес в шину адреса и данные в шину данных. Потом нужно дать разрешение на запись на шине управления.

У процессора есть механизм сохранения инструкций в кэш. Как мы выяснили ранее, за секунду процессор может выполнить миллиарды инструкций. Поэтому если бы каждая инструкция хранилась в ОЗУ, то её изъятие оттуда занимало бы больше времени, чем её обработка. Поэтому для ускорения работы процессор хранит часть инструкций и данных в кэше.

Если данные в кэше и памяти не совпадают, то они помечаются грязными битами (англ. dirty bit).

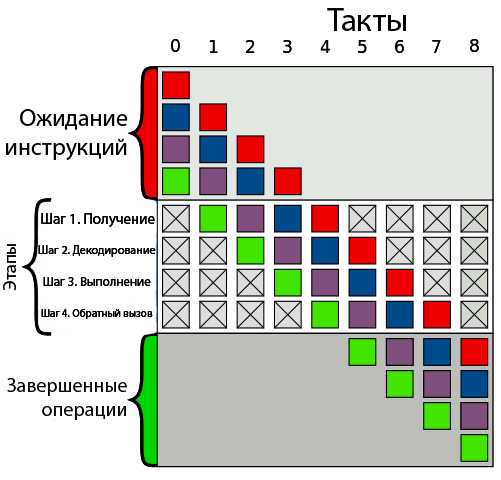

Поток инструкций

Современные процессоры могут параллельно обрабатывать несколько команд. Пока одна инструкция находится в стадии декодирования, процессор может успеть получить другую инструкцию.

Однако такое решение подходит только для тех инструкций, которые не зависят друг от друга.

Если процессор многоядерный, это означает, что фактически в нём находятся несколько отдельных процессоров с некоторыми общими ресурсами, например кэшем.

Процессоры, ядра и потоки. Топология систем

В этой статье я попытаюсь описать терминологию, используемую для описания систем, способных исполнять несколько программ параллельно, то есть многоядерных, многопроцессорных, многопоточных. Разные виды параллелизма в ЦПУ IA-32 появлялись в разное время и в несколько непоследовательном порядке. Во всём этом довольно легко запутаться, особенно учитывая, что операционные системы заботливо прячут детали от не слишком искушённых прикладных программ.

Используемая далее терминология используется в документации процессорам Intel. Другие архитектуры могут иметь другие названия для похожих понятий. Там, где они мне известны, я буду их упоминать.

Цель статьи — показать, что при всём многообразии возможных конфигураций многопроцессорных, многоядерных и многопоточных систем для программ, исполняющихся на них, создаются возможности как для абстракции (игнорирования различий), так и для учёта специфики (возможность программно узнать конфигурацию).

Процессор

Конечно же, самый древний, чаще всего используемый и неоднозначный термин — это «процессор».

В современном мире процессор — это то (package), что мы покупаем в красивой Retail коробке или не очень красивом OEM-пакетике. Неделимая сущность, вставляемая в разъём (socket) на материнской плате. Даже если никакого разъёма нет и снять его нельзя, то есть если он намертво припаян, это один чип.

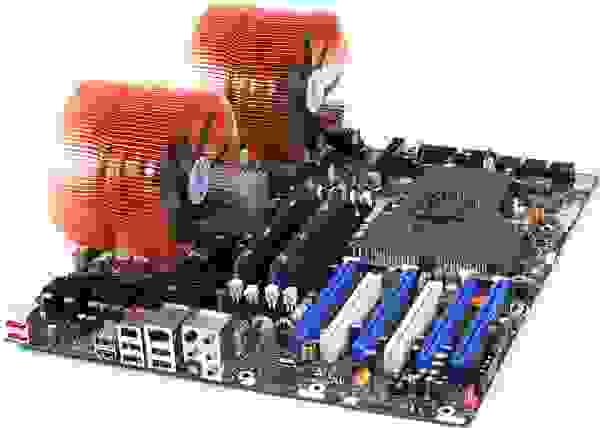

Мобильные системы (телефоны, планшеты, ноутбуки) и большинство десктопов имеют один процессор. Рабочие станции и сервера иногда могут похвастаться двумя или больше процессорами на одной материнской плате.

Поддержка нескольких центральных процессоров в одной системе требует многочисленных изменений в её дизайне. Как минимум, необходимо обеспечить их физическое подключение (предусмотреть несколько сокетов на материнской плате), решить вопросы идентификации процессоров (см. далее в этой статье, а также мою предыдущую заметку), согласования доступов к памяти и доставки прерываний (контроллер прерываний должен уметь маршрутизировать прерывания на несколько процессоров) и, конечно же, поддержки со стороны операционной системы. Я, к сожалению, не смог найти документального упоминания момента создания первой многопроцессорной системы на процессорах Intel, однако Википедия утверждает, что Sequent Computer Systems поставляла их уже в 1987 году, используя процессоры Intel 80386. Широко распространённой поддержка же нескольких чипов в одной системе становится доступной, начиная с Intel® Pentium.

Если процессоров несколько, то каждый из них имеет собственный разъём на плате. У каждого из них при этом имеются полные независимые копии всех ресурсов, таких как регистры, исполняющие устройства, кэши. Делят они общую память — RAM. Память может подключаться к ним различными и довольно нетривиальными способами, но это отдельная история, выходящая за рамки этой статьи. Важно то, что при любом раскладе для исполняемых программ должна создаваться иллюзия однородной общей памяти, доступной со всех входящих в систему процессоров.

К взлёту готов! Intel® Desktop Board D5400XS

Исторически многоядерность в Intel IA-32 появилась позже Intel® HyperThreading, однако в логической иерархии она идёт следующей.

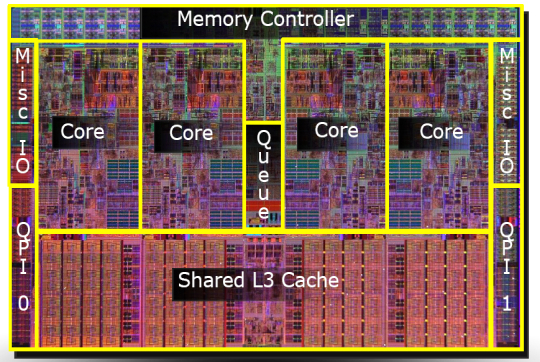

Казалось бы, если в системе больше процессоров, то выше её производительность (на задачах, способных задействовать все ресурсы). Однако, если стоимость коммуникаций между ними слишком велика, то весь выигрыш от параллелизма убивается длительными задержками на передачу общих данных. Именно это наблюдается в многопроцессорных системах — как физически, так и логически они находятся очень далеко друг от друга. Для эффективной коммуникации в таких условиях приходится придумывать специализированные шины, такие как Intel® QuickPath Interconnect. Энергопотребление, размеры и цена конечного решения, конечно, от всего этого не понижаются. На помощь должна прийти высокая интеграция компонент — схемы, исполняющие части параллельной программы, надо подтащить поближе друг к другу, желательно на один кристалл. Другими словами, в одном процессоре следует организовать несколько ядер, во всём идентичных друг другу, но работающих независимо.

Первые многоядерные процессоры IA-32 от Intel были представлены в 2005 году. С тех пор среднее число ядер в серверных, десктопных, а ныне и мобильных платформах неуклонно растёт.

В отличие от двух одноядерных процессоров в одной системе, разделяющих только память, два ядра могут иметь также общие кэши и другие ресурсы, отвечающие за взаимодействие с памятью. Чаще всего кэши первого уровня остаются приватными (у каждого ядра свой), тогда как второй и третий уровень может быть как общим, так и раздельным. Такая организация системы позволяет сократить задержки доставки данных между соседними ядрами, особенно если они работают над общей задачей.

Микроснимок четырёхядерного процессора Intel с кодовым именем Nehalem. Выделены отдельные ядра, общий кэш третьего уровня, а также линки QPI к другим процессорам и общий контроллер памяти.

Гиперпоток

До примерно 2002 года единственный способ получить систему IA-32, способную параллельно исполнять две или более программы, состоял в использовании именно многопроцессорных систем. В Intel® Pentium® 4, а также линейке Xeon с кодовым именем Foster (Netburst) была представлена новая технология — гипертреды или гиперпотоки, — Intel® HyperThreading (далее HT).

Ничто не ново под луной. HT — это частный случай того, что в литературе именуется одновременной многопоточностью (simultaneous multithreading, SMT). В отличие от «настоящих» ядер, являющихся полными и независимыми копиями, в случае HT в одном процессоре дублируется лишь часть внутренних узлов, в первую очередь отвечающих за хранение архитектурного состояния — регистры. Исполнительные же узлы, ответственные за организацию и обработку данных, остаются в единственном числе, и в любой момент времени используются максимум одним из потоков. Как и ядра, гиперпотоки делят между собой кэши, однако начиная с какого уровня — это зависит от конкретной системы.

Я не буду пытаться объяснить все плюсы и минусы дизайнов с SMT вообще и с HT в частности. Интересующийся читатель может найти довольно подробное обсуждение технологии во многих источниках, и, конечно же, в Википедии. Однако отмечу следующий важный момент, объясняющий текущие ограничения на число гиперпотоков в реальной продукции.

Ограничения потоков

В каких случаях наличие «нечестной» многоядерности в виде HT оправдано? Если один поток приложения не в состоянии загрузить все исполняющие узлы внутри ядра, то их можно «одолжить» другому потоку. Это типично для приложений, имеющих «узкое место» не в вычислениях, а при доступе к данным, то есть часто генерирующих промахи кэша и вынужденных ожидать доставку данных из памяти. В это время ядро без HT будет вынуждено простаивать. Наличие же HT позволяет быстро переключить свободные исполняющие узлы к другому архитектурному состоянию (т.к. оно как раз дублируется) и исполнять его инструкции. Это — частный случай приёма под названием latency hiding, когда одна длительная операция, в течение которой полезные ресурсы простаивают, маскируется параллельным выполнением других задач. Если приложение уже имеет высокую степень утилизации ресурсов ядра, наличие гиперпотоков не позволит получить ускорение — здесь нужны «честные» ядра.

Типичные сценарии работы десктопных и серверных приложений, рассчитанных на машинные архитектуры общего назначения, имеют потенциал к параллелизму, реализуемому с помощью HT. Однако этот потенциал быстро «расходуется». Возможно, по этой причине почти на всех процессорах IA-32 число аппаратных гиперпотоков не превышает двух. На типичных сценариях выигрыш от использования трёх и более гиперпотоков был бы невелик, а вот проигрыш в размере кристалла, его энергопотреблении и стоимости значителен.

Другая ситуация наблюдается на типичных задачах, выполняемых на видеоускорителях. Поэтому для этих архитектур характерно использование техники SMT с бóльшим числом потоков. Так как сопроцессоры Intel® Xeon Phi (представленные в 2010 году) идеологически и генеалогически довольно близки к видеокартам, на них может быть четыре гиперпотока на каждом ядре — уникальная для IA-32 конфигурация.

Логический процессор

Из трёх описанных «уровней» параллелизма (процессоры, ядра, гиперпотоки) в конкретной системе могут отсутствовать некоторые или даже все. На это влияют настройки BIOS (многоядерность и многопоточность отключаются независимо), особенности микроархитектуры (например, HT отсутствовал в Intel® Core™ Duo, но был возвращён с выпуском Nehalem) и события при работе системы (многопроцессорные сервера могут выключать отказавшие процессоры в случае обнаружения неисправностей и продолжать «лететь» на оставшихся). Каким образом этот многоуровневый зоопарк параллелизма виден операционной системе и, в конечном счёте, прикладным приложениям?

Далее для удобства обозначим количества процессоров, ядер и потоков в некоторой системе тройкой (x, y, z), где x — это число процессоров, y — число ядер в каждом процессоре, а z — число гиперпотоков в каждом ядре. Далее я буду называть эту тройку топологией — устоявшийся термин, мало что имеющий с разделом математики. Произведение p = xyz определяет число сущностей, именуемых логическими процессорами системы. Оно определяет полное число независимых контекстов прикладных процессов в системе с общей памятью, исполняющихся параллельно, которые операционная система вынуждена учитывать. Я говорю «вынуждена», потому что она не может управлять порядком исполнения двух процессов, находящихся на различных логических процессорах. Это относится в том числе к гиперпотокам: хотя они и работают «последовательно» на одном ядре, конкретный порядок диктуется аппаратурой и недоступен для наблюдения или управления программам.

Чаще всего операционная система прячет от конечных приложений особенности физической топологии системы, на которой она запущена. Например, три следующие топологии: (2, 1, 1), (1, 2, 1) и (1, 1, 2) — ОС будет представлять в виде двух логических процессоров, хотя первая из них имеет два процессора, вторая — два ядра, а третья — всего лишь два потока.

Windows Task Manager показывает 8 логических процессоров; но сколько это в процессорах, ядрах и гиперпотоках?

Linux top показывает 4 логических процессора.

Это довольно удобно для создателей прикладных приложений — им не приходится иметь дело с зачастую несущественными для них особенностями аппаратуры.

Программное определение топологии

Конечно, абстрагирование топологии в единственное число логических процессоров в ряде случаев создаёт достаточно оснований для путаницы и недоразумений (в жарких Интернет-спорах). Вычислительные приложения, желающие выжать из железа максимум производительности, требуют детального контроля над тем, где будут размещены их потоки: поближе друг к другу на соседних гиперпотоках или же наоборот, подальше на разных процессорах. Скорость коммуникаций между логическими процессорами в составе одного ядра или процессора значительно выше, чем скорость передачи данных между процессорами. Возможность неоднородности в организации оперативной памяти также усложняет картину.

Информация о топологии системы в целом, а также положении каждого логического процессора в IA-32 доступна с помощью инструкции CPUID. С момента появления первых многопроцессорных систем схема идентификации логических процессоров несколько раз расширялась. К настоящему моменту её части содержатся в листах 1, 4 и 11 CPUID. Какой из листов следует смотреть, можно определить из следующей блок-схемы, взятой из статьи [2]:

Я не буду здесь утомлять всеми подробностями отдельных частей этого алгоритма. Если возникнет интерес, то этому можно посвятить следующую часть этой статьи. Отошлю интересующегося читателя к [2], в которой этот вопрос разбирается максимально подробно. Здесь же я сначала кратко опишу, что такое APIC и как он связан с топологией. Затем рассмотрим работу с листом 0xB (одиннадцать в десятичном счислении), который на настоящий момент является последним словом в «апикостроении».

APIC ID

В настоящий момент ширина числа, хранящегося в APIC ID, достигла полных 32 бит, хотя в прошлом оно было ограничено 16, а ещё раньше — только 8 битами. Нынче остатки старых дней раскиданы по всему CPUID, однако в CPUID.0xB.EDX[31:0] возвращаются все 32 бита APIC ID. На каждом логическом процессоре, независимо исполняющем инструкцию CPUID, возвращаться будет своё значение.

Выяснение родственных связей

Значение APIC ID само по себе ничего не говорит о топологии. Чтобы узнать, какие два логических процессора находятся внутри одного физического (т.е. являются «братьями» гипертредами), какие два — внутри одного процессора, а какие оказались и вовсе в разных процессорах, надо сравнить их значения APIC ID. В зависимости от степени родства некоторые их биты будут совпадать. Эта информация содержится в подлистьях CPUID.0xB, которые кодируются с помощью операнда в ECX. Каждый из них описывает положение битового поля одного из уровней топологии в EAX[5:0] (точнее, число бит, которые нужно сдвинуть в APIC ID вправо, чтобы убрать нижние уровни топологии), а также тип этого уровня — гиперпоток, ядро или процессор, — в ECX[15:8].

У логических процессоров, находящихся внутри одного ядра, будут совпадать все биты APIC ID, кроме принадлежащих полю SMT. Для логических процессоров, находящихся в одном процессоре, — все биты, кроме полей Core и SMT. Поскольку число подлистов у CPUID.0xB может расти, данная схема позволит поддержать описание топологий и с бóльшим числом уровней, если в будущем возникнет необходимость. Более того, можно будет ввести промежуточные уровни между уже существующими.

Важное следствие из организации данной схемы заключается в том, что в наборе всех APIC ID всех логических процессоров системы могут быть «дыры», т.е. они не будут идти последовательно. Например, во многоядерном процессоре с выключенным HT все APIC ID могут оказаться чётными, так как младший бит, отвечающий за кодирование номера гиперпотока, будет всегда нулевым.

Отмечу, что CPUID.0xB — не единственный источник информации о логических процессорах, доступный операционной системе. Список всех процессоров, доступный ей, вместе с их значениями APIC ID, кодируется в таблице MADT ACPI [3, 4].

Операционные системы и топология

Операционные системы предоставляют информацию о топологии логических процессоров приложениям с помощью своих собственных интерфейсов.

В FreeBSD топология сообщается через механизм sysctl в переменной kern.sched.topology_spec в виде XML:

В MS Windows 8 сведения о топологии можно увидеть в диспетчере задач Task Manager.

Также их предоставляет консольная утилита Sysinternals Coreinfo и API вызов GetLogicalProcessorInformation.

Полная картина

Проиллюстрирую ещё раз отношения между понятиями «процессор», «ядро», «гиперпоток» и «логический процессор» на нескольких примерах.

Система (2, 2, 2)

Система (2, 4, 1)

Система (4, 1, 1)

Прочие вопросы

В этот раздел я вынес некоторые курьёзы, возникающие из-за многоуровневой организации логических процессоров.

Как я уже упоминал, кэши в процессоре тоже образуют иерархию, и она довольно сильно связано с топологией ядер, однако не определяется ей однозначно. Для определения того, какие кэши для каких логических процессоров общие, а какие нет, используется вывод CPUID.4 и её подлистов.

Лицензирование

Некоторые программные продукты поставляются числом лицензий, определяемых количеством процессоров в системе, на которой они будут использоваться. Другие — числом ядер в системе. Наконец, для определения числа лицензий число процессоров может умножаться на дробный «core factor», зависящий от типа процессора!

Виртуализация

Системы виртуализации, способные моделировать многоядерные системы, могут назначить виртуальным процессорам внутри машины произвольную топологию, не совпадающую с конфигурацией реальной аппаратуры. Так, внутри хозяйской системы (1, 2, 2) некоторые известные системы виртуализации по умолчанию выносят все логические процессоры на верхний уровень, т.е. создают конфигурацию (4, 1, 1). В сочетании с особенностями лицензирования, зависящими от топологии, это может порождать забавные эффекты.

Функции и состав процессора: 8ми-16ти разрядный, структура, сопроцессор

Основные функции и состав процессора

Основные функции и состав процессора

На процессор возлагается выполнение операций, предусмотренных его системой команд.

При выполнении программы центральный процессор микропроцессорной системы обеспечивает выполнение всех функций, предусмотренных программной. К ним относится:

Из чего состоит процессор

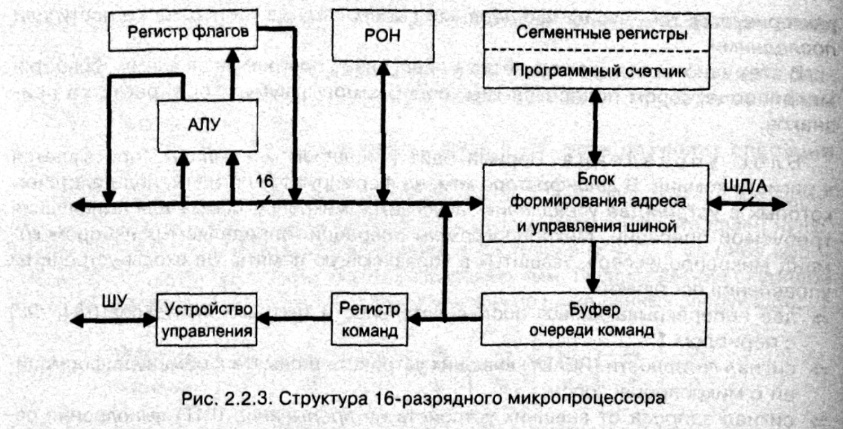

Для выполнения перечисленных функций процессор должен располагать необходимым набором аппаратных средств. Основными функциональными блоками процессора являются (рис. 2.2.1):

В качестве примеров рассмотрим структурно–функциональную организацию 8– и 16–разрядных процессоров.

Состав восьмиразрядного процессора

Для описания основных узлов 8–разрядного процессора воспользуемся рис. 2.2.2, на котором изображена структурная схема процессора 8080 (КР580ВМ80А).

Арифметическо–логическое устройство (АЛУ) позволяет выполнить следующие операции над 8–разрядными операндами:

При выполнении операций один из операндов поступает в АЛУ через аккумулятор А и дополнительный регистр 1, другой операнд — через дополнительный регистр 2. Циклические сдвиги выполняются только над содержимым аккумулятора А. В аккумулятор также помещаются результаты выполненных в АЛУ операций.

Блок десятичной коррекции

При суммировании десятичных чисел может потребоваться коррекция результата, для выполнения которой в микропроцессоре предусмотрен блок десятичной коррекции. При сложении каждый разряд десятичного числа (цифра) представляется четырехразрядным двоичным кодом (полубайтом, тетрадой), например, кодом 8421. Сложение полубайтов происходит по правилам двоичной арифметики. Если сумма больше 9, то возникает необходимость в проведении коррекции. Коррекция осуществляется дополнительным прибавлением двоичного числа 0110 (6) к полученному результату. Это обусловлено тем, что вес пятого разряда двоичного числа составляет 16 десятичных единиц, а вес старшего разряда десятичного числа — 10, т.е. разность равна 6.

Если при сложении получен результат 10… 15, то прибавление числа 6 (0110)2 приведет к появлению 1 в пятом разряде полубайта. Этот разряд «уходит» в старший полубайт и забирает с собой «добавку» (6), оставляя правильный результат. В том случае, когда результат 16… 18, в пятом разряде появляется единица, значение которой (до переноса) соответствует 16 в десятичном исчислении. После переноса единицы пятого разряда в старший полубайт ее значение становится равным 10. Таким образом, перенос сопровождается уменьшением результата на 6 десятичных единиц, что также требует проведения его коррекции. Принцип коррекции иллюстрируется на двух приведенных примерах.

Неправильный результат обнаруживается по наличию единиц в двух старших разрядах (3–й и 2–й), в третьем и первом или по наличию переноса в следующую тетраду.

Регистр признаков

АЛУ непосредственно связано с 5–разрядным регистром признаков (флагов), в котором фиксируется результат выполнения некоторых арифметических и логических операций. Регистр содержит пять триггеров:

Указанные триггеры обеспечивают выполнение в программе условных переходов. Например, если результат выполнения предыдущей операции равен нулю, то триггер нуля устанавливается в единичное состояние (Z = 1), и условие перехода в другую часть программы окажется выполненным. Распределение разрядов регистра признаков условий в байте при передаче по шине данных следующее:

Регистры процессора

Доступ к регистрам, в том числе к счетчику команд и указателю стека, осуществляется через мультиплексоры с помощью селектора регистров.

Регистры общего назначения (РОН) играют роль аккумуляторов, когда в них содержатся обрабатываемые данные, либо указателей, когда в них хранятся адреса операндов. Регистры В, С, D, Е, Н, L могут быть использованы в программе как отдельные 8–разрядные регистры или как 16–разрядные регистровые пары ВС, DE, HL. Название пары В, D, Н всегда соответствует названию первого регистра пары, в котором хранится старший байт 16–разрядного числа. 16–разрядный регистр Н служит адресным регистром: при косвенной регистровой адресации он хранит исполнительный адрес, поступающий из основной памяти.

Регистры W и Z не являются программно доступными и используются для выполнения команд внутри микропроцессора. В них хранятся второй и третий байт команды.

Обмен информацией между микропроцессором и внешними устройствами осуществляется через двунаправленный буферный регистр, а адресация к памяти и внешним устройствам — через 16–разрядный регистр адреса. Особенность буферного и адресного регистров состоит в том, что кроме состояния логического нуля и единицы в них предусмотрено третье состояние, в котором выходное сопротивление регистров бесконечно велико. В этом состоянии микропроцессора внешними устройствами осуществляется прямой доступ к памяти.

Указатель команд, или программный счетчик ( Program Counter — PC).

Счетчик указывает адрес, где находится в памяти очередной байт команды (для команд используются 3–байтовые форматы). Байты команд обычно выбираются в порядке нарастания их адресов. Поэтому после выборки каждого очередного байта схема инкремента–декремента увеличивает содержимое программного счетчика на единицу. Перед началом выборки какой–нибудь команды в счетчик заносится адрес ее первого байта. В процессе выбора 3–байтной команды содержимое счетчика увеличивается трижды. Обычный порядок следования адресов может быть изменен. Для этого в счетчике предусмотрена возможность записи начального адреса той части программы, именуемой подпрограммой, которая должна выполниться.

Указатель стека

Указатель стека (StackPointer —SP) представляет собой 16–разрядный регистр, предназначенный для быстрой адресации особого вида памяти, и именуемой стеком. Стековая память используется при обслуживании прерываний и характеризуется тем, что из нее первыми выбираются данные, которые поступили последними.

В стек заносится адрес возврата к прерванной программе на время обработки микропроцессором подпрограммы, содержимое аккумулятора, регистра признаков.

Блок управления

Первый байт исполняемой команды записывается в регистр команд. В дешифраторе команд формируются сигналы, под действием которых в устройстве управления запускается микропрограмма для выполнения требуемой операции. Микропрограммы операций, определяемых набором команд микропроцессора, «зашиты» в управляющую память. На входы устройства управления поступают:

С выхода устройства управления снимаются сигналы для управления внутренними узлами (на рис. 2.2.3 эти связи не показаны) процессора и внешними устройствами.

Для управления внешними устройствами вырабатываются:

Интерфейс микропроцессора

Обмен информацией между узлами процессора осуществляется по 8–разрядной внутренней шине данных, а с внешней 8–разрядной шиной данных ШД — через буферный регистр. Для адресации к памяти и внешним устройствам используются 16–разрядная шина адреса ША и регистр адреса.

Состав шестнадцатиразрядного микропроцессора

Структурная схема 16–разрядного процессора (8086) изображена на рис. 2.2.3.

Назначение управляющих сигналов

Управляющие сигналы поступают по шине управления ШУ (рис. 2.2.3) микропроцессора (МП), который работает в двух режимах: минимальной и максимальной конфигурации. Сигналы, используемые в обоих режимах:

S6 = 0 при S5 =IF = 1 BHE#/S7 ВНЕ# = 0 подается на старший Н–банк при обращениях к памяти.

S7— сигнал о состоянии процессора, где # — знак инверсии RD# Чтение памяти и порта (в режиме минимальной конфигурации)

TEST# Вывод микросхемы, опрашиваемый командой

WAIT#: при TEST = 1 — режим опроса через 5 тактов; при TEST = 0 — режим ожидания MN/

MX# Переключение режимов минимальной/максимальной конфигурации

В режиме минимальной конфигурации ( MN/ MX = 1) МП вырабатывает следующие управляющие сигналы:

ALE Строб адреса при записи его во внешний буферный регистр

М/IO# Выбор обмена память/порт ВВ

DT/R# Выбор направления обмена или режима записи/чтения

WR# Запись (по фронту) в память или порт ВВ

DEN# Разрешение передачи данных через шину данных

HOLD, HLDA Сигналы запроса на захват шины и подтверждения захвата при прямом доступе к памяти

Сигналы для режима максимальной конфигурации (MN/MX = 0): S2# S1#

S0# Код состояния или типа цикла МП: 000 — подтверждение прерывания; 001 — чтение порта ВВ; 010 — запись в порт ВВ; 011 — останов; 100 — выборка команды; 101 — чтение памяти; 111 — пассивное состояние QS1

QS0 Код состояния очереди: 00 — пассивное состояние (нет операции); 01 — очистка очереди; 10 — выборка первого байта команды; 11 — выборка следующего байта команды RQ/GT1,RQ/GT0

Сигналы запроса на захват шины, разрешения захвата при прямом доступе к памяти и освобождения шины

При обозначении сигналов использован символ #, означающий инверсию, т.е. А# = А.

Рассмотрим несколько подробнее организацию очереди команд и принцип формирования адресов с помощью сегментных регистров.

Организация очереди команд при выполнении программы значительное время расходуется на выборку команд из памяти. Поэтому блок формирования адреса и управления шиной старается поддерживать заполненным буфер очереди команд, считывая из памяти последующие команды во время выполнения текущей команды, когда ШД/А остается свободной.

После завершения текущей команды следующая команда считывается из буфера. Так как не требуется обращения к памяти, повышается быстродействие процессора. При выполнения команд условных и безусловных переходов, связанных с передачей управления другой ячейке памяти, происходит очистка буфера, после чего он начинает заполняться вновь.

Принцип формирования адресов

Поставим задачу сформировать 20–разрядный адрес (addr20), обеспечивающий доступ к 2 20 = 1М байт памяти, с помощью двух 16–разрядных регистров. Каждый из 16–разрядных регистров обеспечивает доступ к 2 16 ячейкам или к 64К байт памяти. Поэтому выделим в 1М байт памяти сегмент емкостью 64К байт с условием, чтобы младший разряд его шестнадцатеричного кода начального адреса был равен нулю, т. е. код адреса имел вид ХХХХ0

h, где X = 0 или 1, h — обозначение 16–ричного кода (hexadecimal). Один из регистров выберем в качестве селектора сегмента(sel), другой — в качестве регистра смещения (offset). Представим адрес в виде суммы addr20 = 1 6 x sel +offset =XXXX0h +YYYYh.

На рис. 2.2.4, а показано, как можно обеспечить доступ к памяти с числом ячеек 2 20 (или емкостью 1 M байт при использовании однобайтных ячеек).

В качестве селектора, который можно рассматривать как указатель сегмента, в процессорах используются сегментные регистры (регистры кода CS, стека SS, данных DS и дополнительный регистр ES), а в качестве регистров смещения — регистры общего назначения (программный счетчик IP, указатель стека SP, указатель базы BP и регистры автоинкрементной SI и автодекрементной DI адресации). Возможны следующие пары регистров:

ES DI. На рис. 2.2.4, б показана в качестве примера реализация принципа адресации с использованием пары

О сопроцессорах

Для расширения функциональных возможностей и повышения производительности центрального процессора микропроцессорная система может содержать дополнительные процессоры, или сопроцессоры. Например, в первых поколениях компьютеров для расширения функций центрального процессора 80286 использовался сопроцессор 80287.

Сопроцессор 80287 предназначен для выполнения операций над числами с плавающей точкой (запятой), которые потребовали бы от основного процессора больших затрат машинного времени. Поэтому такой сопроцессор называют числовым процессором, процессором для обработки числовых данных, процессором

NDP (Numeric Data Processor) или математическим сопроцессором. Сопроцессор выполняет такие сложные операции, как деление длинных операндов, вычисление тригонометрических функций, извлечение квадратного корня и нахождение логарифма в 10–100 раз быстрее основного процессора. Точность результатов расчетов значительно выше точности, обеспечиваемой вычислительными модулями, входящими в состав самих процессоров. Выигрыш реализуется только при выполнении программ, написанных с учетом на совместное использование сопроцессора с основным процессором. При совместной работе операции сложения, вычитания и умножения выполняются основным процессором и не передаются сопроцессору.

Сопроцессор имеет собственную систему команд (инструкций), которая отличается от системы команд процессора. Выполняемая программа должна сама определять наличие сопроцессора и после этого использовать написанные для него инструкции. Большинство программ, рассчитанных на использование сопроцессоров, обнаруживают его присутствие и используют предоставляемые возможности.

Наиболее эффективно сопроцессоры используются в программах со сложными математическими расчетами: в электронных таблицах, базах данных, статистических программах и системах автоматизированного проектирования. При работе с текстовыми редакторами сопроцессор не используется.

В процессорах 80486 и более поздних моделях используются встроенные сопроцессоры. Они выполняются в виде устройства с плавающей точкой (Floating Point Unit — FPU), входящего в состав процессора, и располагаются на том же кристалле. Инструкции над числами с плавающей точкой входят в систему команд процессора.

Внутренние ресурсы процессора

Архитектура процессоров предоставляет наиболее часто требуемые типы данных, регистры и режимы адресации. Каждый процессор поддерживает несколько типов данных, режимов адресации и содержит определенный набор внутренних регистров.

Разнообразие, доступность и умелое использование ресурсов способствует повышению производительности системы. Недостающие или отсутствующие ресурсы допускают программное моделирование, но снижают производительность.

Для разработки системной программы используются жестко связанные с архитектурой процессора системные ресурсы, к которым относят адреса памяти и ввода/вывода, запросы прерываний и каналы прямого доступа к памяти. Они обеспечивают управление виртуальной памятью, мультизадачностью и средствами защиты. Системные ресурсы образуют основу возможностей защищенного режима.

Основные функции и состав процессора

Основные функции и состав процессора